Die 3nm „Pessimism Wall“ – Versteckte Kosten im modernen Chipdesign

30. März 2026

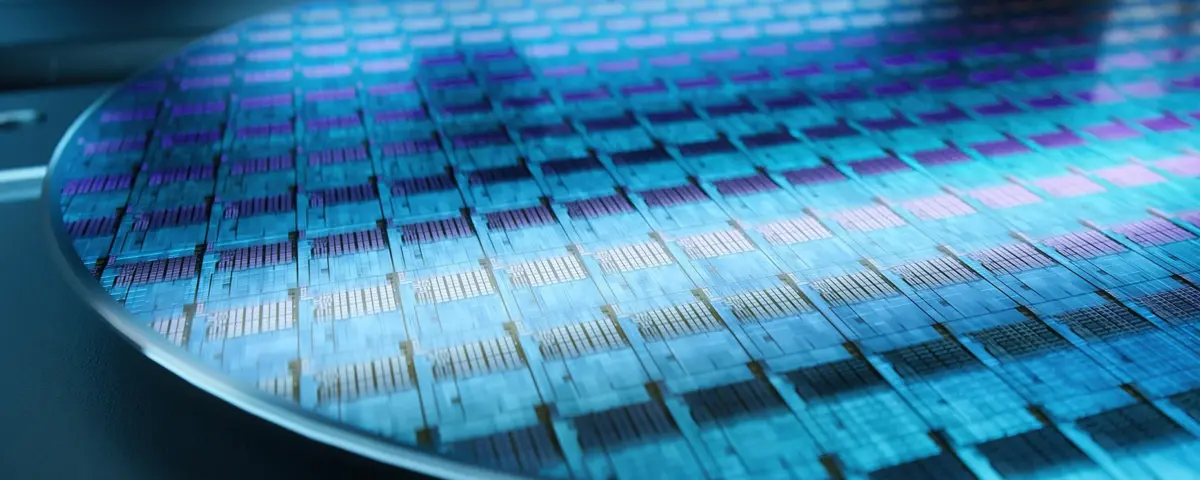

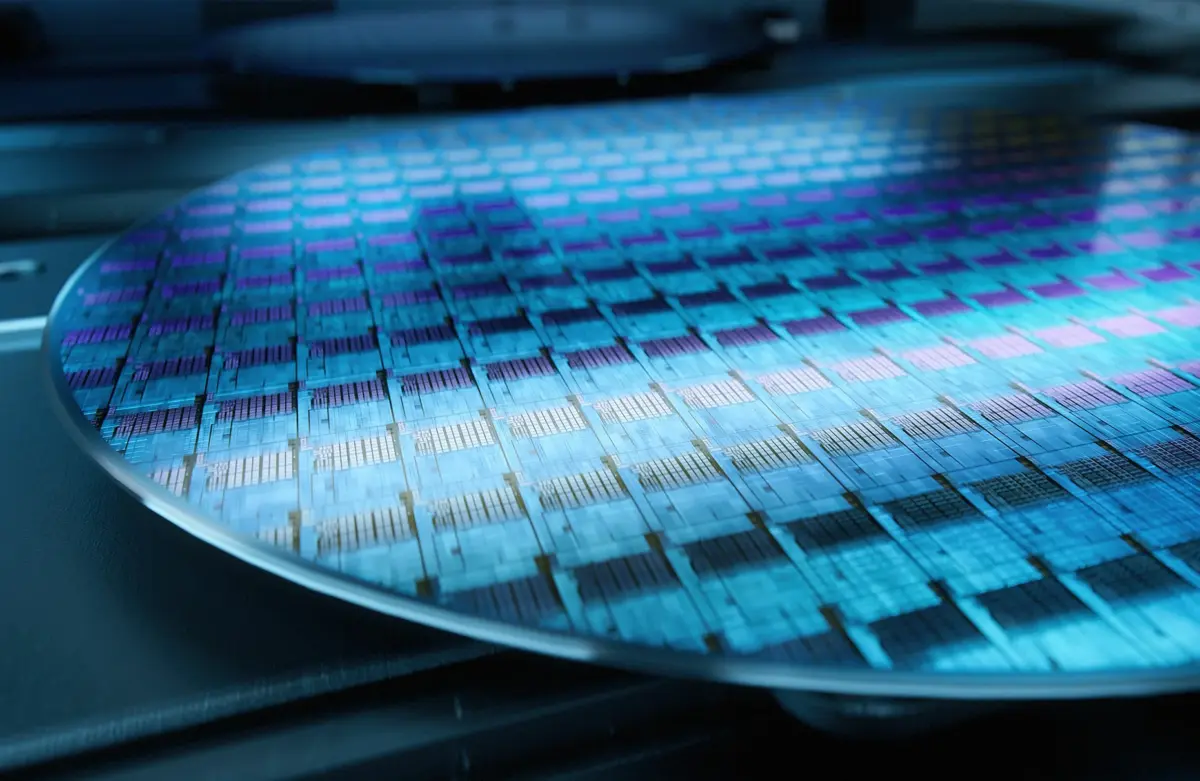

Mit dem Eintritt der Halbleiterindustrie in das 3nm-Zeitalter liegt der Fokus häufig auf Architektur, Performance und Energieeffizienz. Ein entscheidender Faktor rückt dabei jedoch zunehmend in den Hintergrund: Wafer-Beschaffung und Materialqualität.

Während Designmethoden mit Herausforderungen wie der „Pessimism Wall“ und schrumpfenden Margen kämpfen, spielt die physische Grundlage jedes Chips – der Wafer selbst – eine zentrale Rolle für die tatsächliche Performance im Einsatz.

Warum Waferqualität bei 3nm noch wichtiger ist

Bei fortschrittlichen Technologienodes stehen Designmargen bereits unter starkem Druck. Jede zusätzliche Variabilität auf Wafer-Ebene wirkt sich direkt aus auf:

- Timing-Stabilität

- Leistungsaufnahme

- Yield und Zuverlässigkeit

Parameter, die früher als beherrschbar galten – wie Dickenvariation (TTV), Ebenheit oder Oberflächenqualität – haben heute einen deutlich größeren Einfluss auf das Bauteilverhalten.

Bei 3nm können selbst kleinste Abweichungen messbare Performance-Unterschiede verursachen.

Der Zusammenhang zwischen Designmargen und Materialvariabilität

Moderne Chipdesigns kompensieren Unsicherheiten häufig durch konservative Margen. Doch nicht alle Unsicherheiten stammen aus Designmodellen – ein wesentlicher Teil entsteht durch Materialvariationen und Prozessschwankungen.

Zu den wichtigsten waferbezogenen Einflussfaktoren zählen:

- Uniformität: Schwankungen in Dicke oder Dotierung beeinflussen elektrische Eigenschaften über den gesamten Wafer

- Oberflächenqualität: Defekte oder Partikel reduzieren den Yield, insbesondere bei stark skalierten Strukturen

- Thermische Oxidqualität: Abweichungen wirken sich direkt auf Zuverlässigkeit und Performance aus

- Batch-to-Batch-Stabilität: Inkonsistente Lieferungen erhöhen den Bedarf an zusätzlichen Design-Sicherheitsmargen

Eine Reduzierung dieser Variabilität kann daher unmittelbar dazu beitragen, unnötige Designmargen zu minimieren.

Druck auf die Lieferkette bei Advanced Nodes

Im 3nm-Bereich wird die Halbleiter-Lieferkette komplexer und weniger flexibel:

- Begrenzte Anzahl qualifizierter Hersteller

- Höhere Anforderungen an Qualifikation und Freigabeprozesse

- Längere Lieferzeiten bei gleichzeitig engeren Spezifikationen

Zuverlässige Beschaffung und starke Lieferantennetzwerke sind daher wichtiger denn je. Verzögerungen oder Inkonsistenzen bei der Waferlieferung können nicht nur die Produktion, sondern auch Designvalidierung und Ramp-up-Phasen erheblich beeinflussen.

Ein strategischer Ansatz für die Wafer-Beschaffung

Um Advanced-Node-Projekte erfolgreich umzusetzen, sollten Unternehmen ihre Beschaffungsstrategie gezielt weiterentwickeln:

- Zusammenarbeit mit qualifizierten und bewährten Herstellern

- Sicherstellung enger Spezifikationskontrolle und vollständiger Rückverfolgbarkeit

- Aufbau flexibler Lieferstrukturen zur Abdeckung von Nachfrageschwankungen

- Abstimmung der Waferspezifikationen auf reale Designanforderungen – nicht nur auf Standardwerte

Eine enge Zusammenarbeit zwischen Designteams, Fabs und Lieferanten ist entscheidend, um Risiken zu reduzieren und die Effizienz zu steigern.

Wie die ABC GmbH Advanced-Node-Projekte unterstützt

Die ABC GmbH ist spezialisiert auf die Beschaffung hochwertiger Siliziumwafer über ein globales Netzwerk qualifizierter Fertigungspartner.

Unser Ansatz basiert auf:

- Flexibilität: Individuell angepasste Waferspezifikationen entsprechend den Kundenanforderungen

- Qualitätssicherung: Strenge Lieferantenqualifikation und vollständige Traceability

- Globale Beschaffung: Zugang zu mehreren Herstellern zur Sicherstellung der Versorgung

- Value-Added Services: Beschichtungen, Reclaim, Dünnen, Schneiden und Laser-Markierung

Damit unterstützen wir unsere Kunden dabei, Variabilität zu reduzieren, Prozessstabilität zu erhöhen und die Anforderungen moderner Technologienodes zuverlässig zu erfüllen.